# HIGH GAIN LOW POWER OPERATIONAL AMPLIFIER DESIGN AND COMPENSATION TECHNIQUES

by

Lisha Li

A dissertation submitted to the faculty of

Brigham Young University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

Brigham Young University

April 2007

Copyright © 2007 Lisha Li

All Rights Reserved

# BRIGHAM YOUNG UNIVERSITY

## GRADUATE COMMITTEE APPROVAL

of a dissertation submitted by

# Lisha Li

This dissertation has been read by each member of the following graduate committee and by majority vote has been found to be satisfactory.

| Date | Donald T. Comer, Chair |

|------|------------------------|

| Date | David J. Comer         |

| Date | Doran K. Wilde         |

| Date | Richard L. Frost       |

| Date | D. J. Lee              |

## BRIGHAM YOUNG UNIVERSITY

As chair of the candidate's graduate committee, I have read the dissertation of Lisha Li in its final form and have found that (1) its format, citations, and bibliographical style are consistent and acceptable and fulfill university and department style requirements; (2) its illustrative materials including figures, tables, and charts are in place; and (3) the final manuscript is satisfactory to the graduate committee and is ready for submission to the university library.

Date

Donald T. Comer Chair, Graduate Committee

Accepted for the Department

Michael J. Wirthlin Graduate Coordinator

Accepted for the College

Alan R. Parkinson Dean, Ira A. Fulton College of Engineering and Technology

### ABSTRACT

# HIGH GAIN LOW POWER OPERATIONAL AMPLIFIER DESIGN AND COMPENSATION TECHNIQUES

Lisha Li

Department of Electrical and Computer Engineering

Doctor of Philosophy

This dissertation discusses and compares the existing compensation methods for operational amplifiers. It explores a method to stabilize the op amps without sacrificing bandwidth to the same degree that commonly used methods do. A creative design methodology combining intuition, mathematical analysis, and mixed level simulation is explored for the new compensation scheme. The mixed level approach, associating system level simulation for most circuits along with device level simulation for some critical analog circuit paths, is presented to verify the behavior of new design concepts in an effective way. This approach also provides sufficient accuracy to predict the circuit performance realistically. The new feedforward compensation method overcomes the serious drawback of the widely used pole splitting method, which greatly narrows the bandwidth. It can improve the phase margin as well as optimize the bandwidth of the op amp. The proposed feedforward compensation method can be easily applied to the popular two gain stage op amp architectures with very little alteration.

MOS devices are used in the weak inversion region or the subthreshold inversion region to minimize dc source power. A feasible configuration for high gain, low power op amp design utilizing subthreshold operation along with active operation is proposed. This op amp uses composite cascode connections for the differential input stage, a common source second stage, and a current mirror. A prototype of the op amp was fabricated in a 0.25  $\mu$ m CMOS process. The proposed op amp produces an open loop gain above one million with low power consumption around 110  $\mu$ W and shows a favorable slew rate and GBW product compared to other amplifiers driving large capacitive loads. In addition, the composite cascode amplifier requires a compensation capacitor of only 3.5 pF which allows a very small op amp cell. This design is intended for applications where simplicity of layout, small cell size, and low power are important. The open loop gain of this design is comparable to bipolar op amps and exceeds all known reported CMOS designs using the classic Widlar architecture. The fabricated op amp test results show that the BSIM3 model in CADENCE Spectre Spice Simulation matches closely to the experimental results in spite of the low current weak inversion operation of the composite cascode output device and thus provide confidence in the simulation for other similar designs. While facing the challenge of measuring the op amp open loop characteristics at decreased power supply voltages, a few viable techniques were developed to measure the op amp open loop parameters using typically available bench test equipment.

#### ACKNOWLEDGMENTS

I would like to express my sincere appreciation to Dr. Donald T. Comer, my advisor, for his great mentoring and support over all these years to help me complete my research and study at Brigham Young University. His guidance contributes greatly to this dissertation. His sharp insights of circuit techniques and encouragement for having a passion for creative circuit design, have been crucial to my success at BYU and will benefit my upcoming career. I would like to thank Dr. David J. Comer for the knowledge that I have learned from his circuit courses, the bright ideas shared with me, and the many inspiration. I would also like to acknowledge the influence and help of the rest of my doctoral committee - Dr. Doran K. Wilde, Dr. D. J. Lee, and Dr. Richard L. Frost. Also, I would like to thank the other members of the Analog and Mixed-Signal Laboratory at BYU over the years, for their friendship, discussion, and help. I would like to thank Kent Layton specifically for his suggestion and help in the chip testing process.

Lastly, I want to express my deep gratitude to my dear parents and sister for their unconditional love and unfailing support for the many years. Without their love and support, I will not be able to get through the difficulties encountered and finish what I want to do.

# Table of Contents

| A        | ckno  | wledge                                                              | ements                                                            | xiii |

|----------|-------|---------------------------------------------------------------------|-------------------------------------------------------------------|------|

| Li       | st of | Table                                                               | S                                                                 | xxi  |

| Li       | st of | Figur                                                               | es                                                                | xxv  |

| 1        | Intr  | oduct                                                               | ion                                                               | 1    |

|          | 1.1   | Resea                                                               | rch Contributions                                                 | 4    |

|          | 1.2   | Disser                                                              | tation Outline                                                    | 6    |

| <b>2</b> | Free  | quency                                                              | Compensation Techniques                                           | 9    |

|          | 2.1   | Introd                                                              | luction                                                           | 9    |

|          | 2.2   | Feedb                                                               | ack Circuit Theory                                                | 9    |

|          | 2.3   | Stabil                                                              | ity of Feedback Systems                                           | 14   |

|          | 2.4   | 4 Basic Frequency Compensation Techniques of Operational Amplifiers |                                                                   | 17   |

|          |       | 2.4.1                                                               | Parallel Compensation                                             | 17   |

|          |       | 2.4.2                                                               | Pole Splitting - Single Miller Compensation (SMC) $\ . \ . \ .$ . | 18   |

|          | 2.5   | Other                                                               | Multistage Operational Amplifier Compensation Techniques          | 19   |

|          |       | 2.5.1                                                               | Nested Miller Compensation (NMC) and the Variants                 | 20   |

|          |       | 2.5.2                                                               | Single Miller FeedForward Compensation (SMFFC) $\ldots$ .         | 23   |

|          |       | 2.5.3                                                               | Nonstandard NMC Schemes                                           | 24   |

|          |       | 2.5.4                                                               | No Capacitor Feed Forward (NCFF)                                  | 25   |

|          |       | 2.5.5                                                               | Negative Miller Capacitance Compensation (NMCC)                   | 26   |

|   | 2.6                  | Conclu                                                                                           | sion                                                                                 | 26 |

|---|----------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----|

| 3 | $\operatorname{Cre}$ | ative I                                                                                          | Feedforward Op amp Compensation Design                                               | 29 |

|   | 3.1                  | Introd                                                                                           | uction                                                                               | 29 |

|   | 3.2                  | Config                                                                                           | puration of the Feedforward Compensation Op amp                                      | 31 |

|   |                      | 3.2.1                                                                                            | Design Methodology                                                                   | 33 |

|   |                      | 3.2.2                                                                                            | System Analysis of Feedforward Compensation                                          | 33 |

|   | 3.3                  | Stabili                                                                                          | ty Analysis                                                                          | 35 |

|   |                      | 3.3.1                                                                                            | Damping Analysis                                                                     | 38 |

|   |                      | 3.3.2                                                                                            | Maximally Flat Response                                                              | 39 |

|   | 3.4                  | Freque                                                                                           | ency and Transient Domain Simulation                                                 | 39 |

|   |                      | 3.4.1                                                                                            | Example 1 - Conventional Feedback Amplifier (Uncompensated)                          | 40 |

|   |                      | 3.4.2                                                                                            | Example 2 - Pole Splitting (Simple Miller Capacitor Compen-<br>sation)               | 41 |

|   |                      | 3.4.3                                                                                            | Example 3 - Proposed Active Feedforward                                              | 42 |

|   | 3.5                  | Open                                                                                             | Loop Analysis                                                                        | 44 |

|   | 3.6                  | 6 Generic Op amp Device Simulation Results                                                       |                                                                                      |    |

|   | 3.7                  | <sup>7</sup> Modified Feedforward Compensation Model Including The Lead And<br>Lead-lag Circuits |                                                                                      |    |

|   | 3.8                  | Design                                                                                           | a of the $g_m$ with the Lead-lag Circuit $\ldots \ldots \ldots \ldots \ldots \ldots$ | 52 |

|   | 3.9                  | Conclu                                                                                           | asion                                                                                | 52 |

| 4 | Low                  | v Volta                                                                                          | ge Low Power Op Amp Gain Boosting Techniques                                         | 55 |

|   | 4.1                  | Introd                                                                                           | uction                                                                               | 55 |

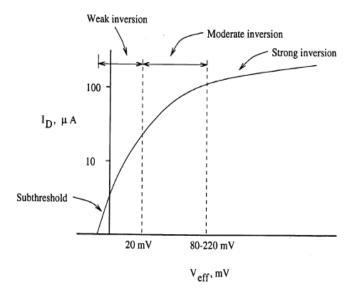

|   | 4.2                  | MOSF                                                                                             | ET Operation                                                                         | 57 |

|   |                      | 4.2.1                                                                                            | Strong Inversion Region                                                              | 58 |

|   |                      | 4.2.2                                                                                            | Moderate Inversion Region                                                            | 59 |

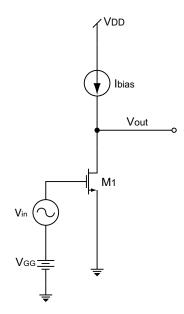

|   |                                                                  | 4.2.3                 | Weak Inversion Region                                                                           | 60 |

|---|------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------|----|

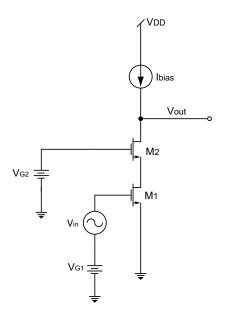

|   | 4.3                                                              | The C                 | Conventional Cascode Connection                                                                 | 61 |

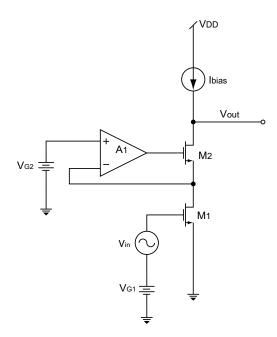

|   | 4.4                                                              | Other                 | Cascode Techniques                                                                              | 63 |

|   |                                                                  | 4.4.1                 | Gain Boosted Cascode Amplifier                                                                  | 63 |

|   |                                                                  | 4.4.2                 | Folded Cascode Connection                                                                       | 65 |

|   | 4.5                                                              | Other                 | Low Supply Voltage Techniques                                                                   | 67 |

|   |                                                                  | 4.5.1                 | Composite Cascode                                                                               | 68 |

|   |                                                                  | 4.5.2                 | Bulk-Driven Devices                                                                             | 68 |

|   |                                                                  | 4.5.3                 | Floating Gate MOS                                                                               | 71 |

|   | 4.6                                                              | Conclu                | usion $\ldots$ | 73 |

| 5 | 5 Design of High Gain Op Amp Using Composite Cascode Connections |                       |                                                                                                 |    |

|   | 5.1                                                              | Introd                | luction                                                                                         | 75 |

|   | 5.2                                                              | The C                 | Composite Cascode Connection                                                                    | 76 |

|   | 5.3                                                              | Practi                | ical Composite Cascode Circuit                                                                  | 78 |

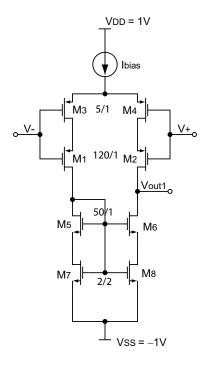

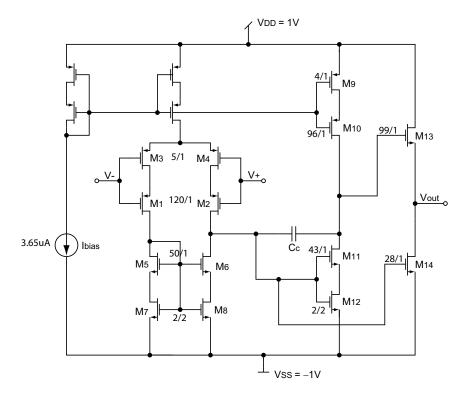

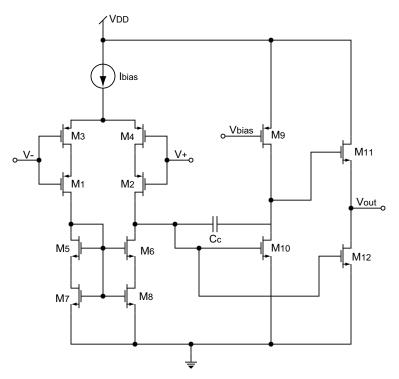

|   | 5.4                                                              | 4 Circuit Realization |                                                                                                 | 79 |

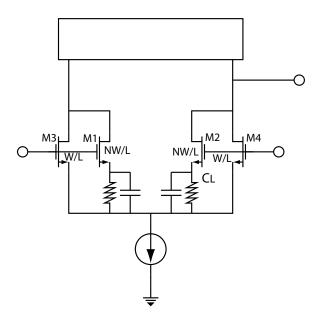

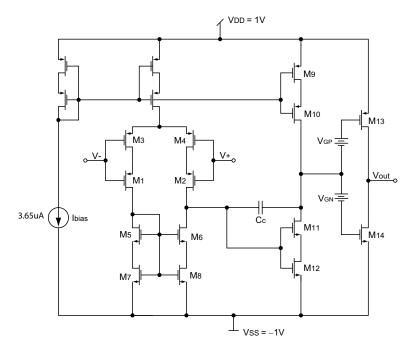

|   |                                                                  | 5.4.1                 | Input Differential Composite Cascode Stage                                                      | 80 |

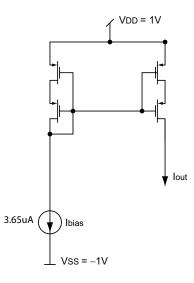

|   |                                                                  | 5.4.2                 | Composite Cascode Current Mirror                                                                | 81 |

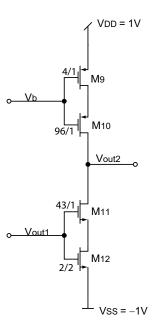

|   |                                                                  | 5.4.3                 | Second Composite Cascode Stage                                                                  | 81 |

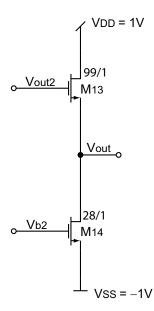

|   |                                                                  | 5.4.4                 | Output Source Follower With A Current-sink Load                                                 | 83 |

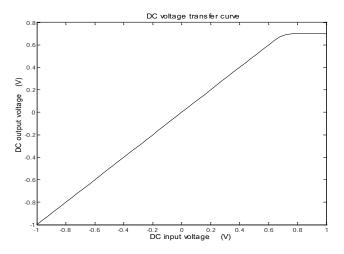

|   |                                                                  | 5.4.5                 | Composite Cascode Op Amp in Widlar Architecture                                                 | 84 |

|   |                                                                  | 5.4.6                 | Total Harmonic Distortion                                                                       | 86 |

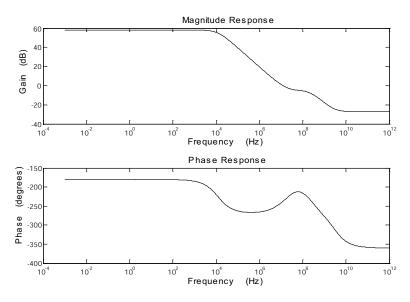

|   | 5.5                                                              | Simple                | e Miller Compensation (Pole Splitting)                                                          | 86 |

|   | 5.6                                                              | Simula                | ation and Experimental Results                                                                  | 87 |

|   | 5.7                                                              | Layou                 | t Design                                                                                        | 90 |

|   | 5.8 | Differe | ent Configurations of Various Composite Cascode Op<br>Amp $\ldots$ .           | 91  |

|---|-----|---------|--------------------------------------------------------------------------------|-----|

|   | 5.9 | Concl   | usion                                                                          | 93  |

| 6 | Op  | Amp '   | Test Procedure and Methods                                                     | 95  |

|   | 6.1 | Introd  | luction                                                                        | 95  |

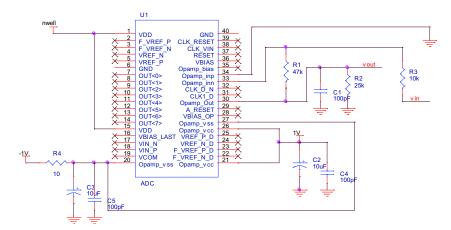

|   | 6.2 | Power   | Supply Current Test and Debugging                                              | 96  |

|   | 6.3 | Op an   | np Test Setup                                                                  | 100 |

|   | 6.4 | Op Ai   | mp Closed Loop Characteristic Test Configuration                               | 101 |

|   | 6.5 | Opam    | p Open Loop Gain Test Methods                                                  | 102 |

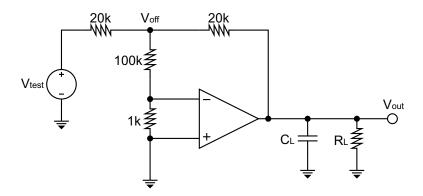

|   |     | 6.5.1   | Measurement Strategy One                                                       | 103 |

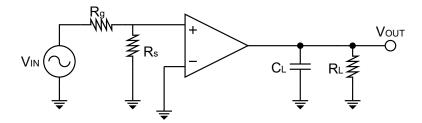

|   |     | 6.5.2   | Measurement Strategy Two                                                       | 105 |

|   |     | 6.5.3   | Measurement Strategy Three                                                     | 106 |

|   |     | 6.5.4   | Measurement Strategy Four                                                      | 107 |

|   | 6.6 | Comp    | osite Cascode Op Amp Chip Test Results                                         | 108 |

|   | 6.7 | Concl   | usion                                                                          | 109 |

| 7 | Cor | nclusio | n and Future Research                                                          | 111 |

|   | 7.1 | Contr   | ibutions                                                                       | 112 |

|   |     | 7.1.1   | Current Compensation Methods Investigation                                     | 112 |

|   |     | 7.1.2   | Feedforward Compensation Method                                                | 113 |

|   |     | 7.1.3   | System-Level and Combined Device/Transfer Function Simula-<br>tion Methodology | 113 |

|   |     | 7.1.4   | Stability Analysis of the Feedforward Architecture                             | 113 |

|   |     | 7.1.5   | MOSFET in Subthreshold Inversion Used for Low Power Op<br>Amp Designs          | 113 |

|   |     | 7.1.6   | Architecture of A High gain Composite Cascode Operational<br>Amplifier         | 114 |

|              | 7.1.7  | Modified Composite Cascode Operational Amplifiers for Differ-<br>ent Applications | 114 |

|--------------|--------|-----------------------------------------------------------------------------------|-----|

|              | 7.1.8  | Practical Test Methods of High Gain Op Amps                                       | 115 |

| 7.2          | Future | Research                                                                          | 115 |

| Bibliography |        |                                                                                   |     |

# List of Tables

| 3.1 | Routh Array                                                                      | 36  |

|-----|----------------------------------------------------------------------------------|-----|

| 3.2 | The Routh Array of Proposed Feedforward Compensation $\ldots \ldots$             | 37  |

| 3.3 | Compensation Method Performance Comparison                                       | 48  |

| 3.4 | Simulation Result Of Modified Feedforward Compensation with Lead-Lag             | 51  |

| 5.1 | Opamp Simulation Results and Test Results                                        | 90  |

| 6.1 | The test results of the current of the op amp chip $\ldots \ldots \ldots \ldots$ | 98  |

| 6.2 | Opamp Test Results                                                               | 108 |

# List of Figures

| 2.1  | General negative feedback system                                      | 10 |

|------|-----------------------------------------------------------------------|----|

| 2.2  | Phase Margin Plot                                                     | 16 |

| 2.3  | SMC                                                                   | 18 |

| 2.4  | SMCNR                                                                 | 19 |

| 2.5  | NMC                                                                   | 20 |

| 2.6  | RNMC                                                                  | 21 |

| 2.7  | MNMC                                                                  | 22 |

| 2.8  | NGCC                                                                  | 22 |

| 2.9  | SMFFC                                                                 | 24 |

| 2.10 | NCFF                                                                  | 25 |

| 3.1  | The phase diagram of feedforward                                      | 32 |

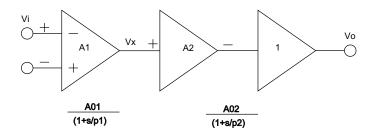

| 3.2  | The block circuit of feedforward                                      | 32 |

| 3.3  | The typical two-stage operational amplifier model                     | 34 |

| 3.4  | Simplified model of the feedforward compensated operational amplifier | 34 |

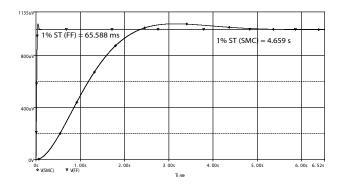

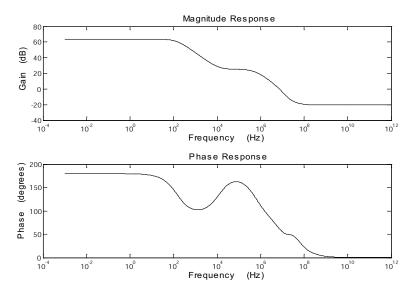

| 3.5  | Uncompensated responses in frequency domain and time domain           | 41 |

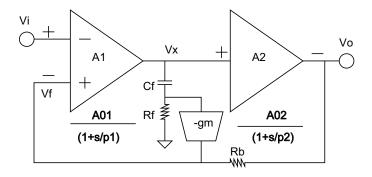

| 3.6  | Frequency Responses of SMC and FF                                     | 43 |

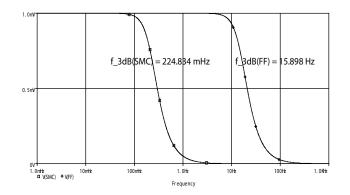

| 3.7  | Settling Time of Feedback Op Amp Step Response                        | 43 |

| 3.8  | Step Responses of SMC and FF                                          | 44 |

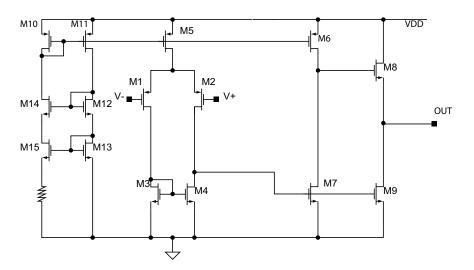

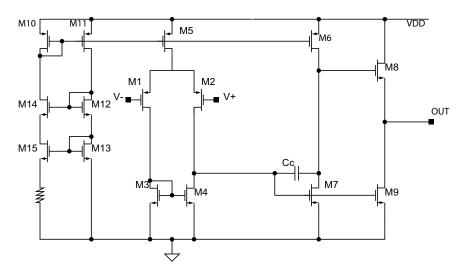

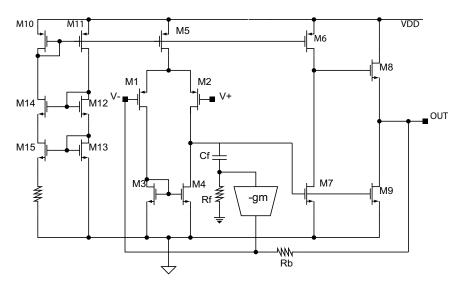

| 3.9  | A classical two gain stage op amp                                     | 46 |

| 3.10 | SMC compensated op amp                                                | 47 |

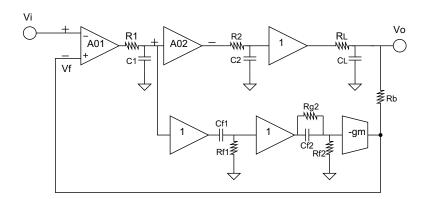

| 3.11 | Feedforward compensated op amp                                                                                                                               | 48 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

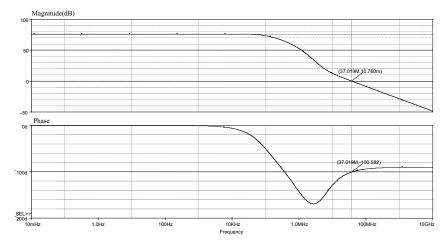

| 3.12 | Frequency response of the feedforward model                                                                                                                  | 49 |

| 3.13 | Modified feedforward compensation system model                                                                                                               | 50 |

| 3.14 | Frequency response of the modified feedforward method                                                                                                        | 51 |

| 3.15 | Creative $g_m$ design $\ldots \ldots \ldots$ | 52 |

| 4.1  | Power supply and threshold voltage versus the MOSFET channel length [1]                                                                                      | 56 |

| 4.2  | Operation regions of an MOS transistor $[2]$                                                                                                                 | 58 |

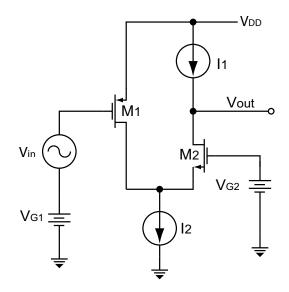

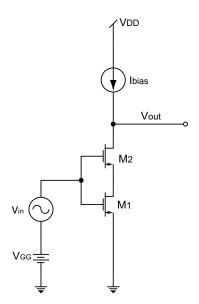

| 4.3  | Single stage amplifier                                                                                                                                       | 60 |

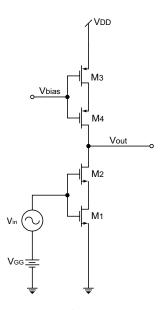

| 4.4  | Conventional cascode amplifier                                                                                                                               | 62 |

| 4.5  | Gain boosted cascode amplifier                                                                                                                               | 64 |

| 4.6  | Simple folded cascode circuit                                                                                                                                | 65 |

| 4.7  | Folded cascode op amp structure                                                                                                                              | 66 |

| 4.8  | bulk-driven amplifier                                                                                                                                        | 69 |

| 4.9  | Floating gate transistor                                                                                                                                     | 71 |

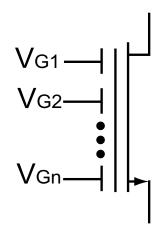

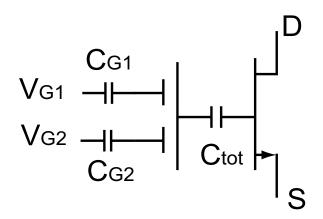

| 4.10 | Two input floating gate transistor                                                                                                                           | 72 |

| 5.1  | Composite cascode amplifier                                                                                                                                  | 77 |

| 5.2  | Practical composite cascode stage                                                                                                                            | 78 |

| 5.3  | Op amp input differential composite cascode stage                                                                                                            | 80 |

| 5.4  | Op amp input stage frequency response                                                                                                                        | 81 |

| 5.5  | Op amp composite cascode current mirror                                                                                                                      | 82 |

| 5.6  | Op amp second composite cascode stage                                                                                                                        | 82 |

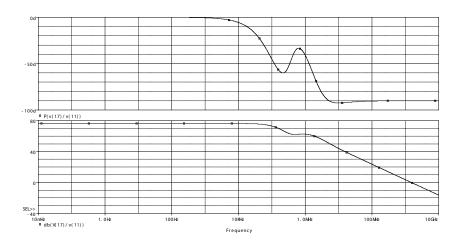

| 5.7  | Op amp second stage frequency response                                                                                                                       | 83 |

| 5.8  | Op amp output source follower stage                                                                                                                          | 84 |

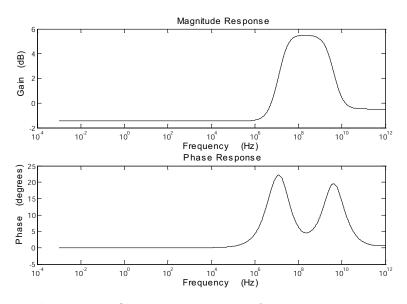

| 5.9  | Op amp output stage frequency response                                                                                                                       | 84 |

| 5.10 | Composite cascode op amp                                                                                       | 85  |

|------|----------------------------------------------------------------------------------------------------------------|-----|

| 5.11 | Composite cascode op amp DC transfer characteristic                                                            | 86  |

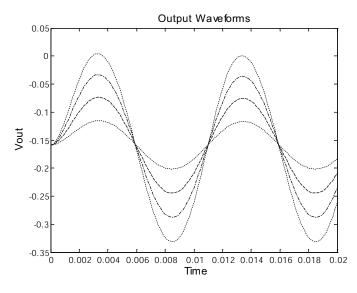

| 5.12 | Op amp waveforms                                                                                               | 87  |

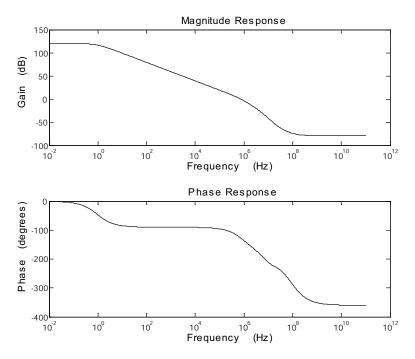

| 5.13 | SMC compensated op amp open loop response                                                                      | 88  |

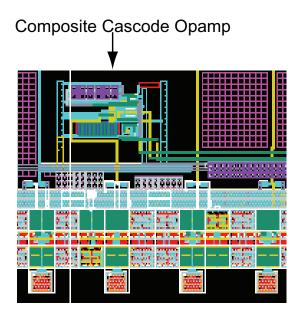

| 5.14 | Fabricated composite cascode op amp                                                                            | 89  |

| 5.15 | Op amp with input differential composite cascode stage and regular common source second stage                  | 92  |

| 5.16 | Op amp with two composite cascode gain stages and a class AB output stage                                      | 93  |

| 6.1  | The interconnection of the chip $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 97  |

| 6.2  | Debugging circuit setting                                                                                      | 97  |

| 6.3  | ESD circuit                                                                                                    | 100 |

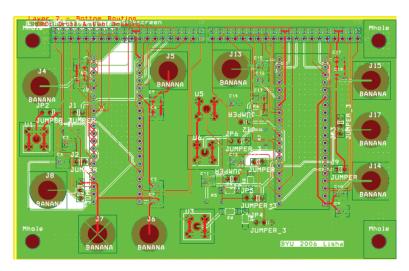

| 6.4  | The PCB layout                                                                                                 | 101 |

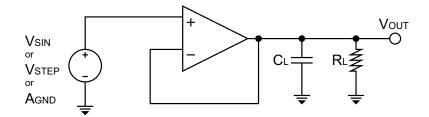

| 6.5  | Op amp unit feedback configuration                                                                             | 102 |

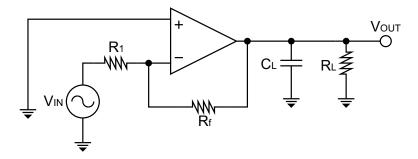

| 6.6  | Op amp gain bandwidth configuration                                                                            | 102 |

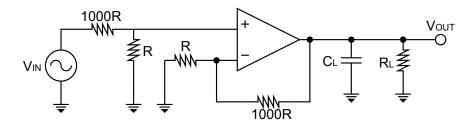

| 6.7  | Op amp open loop gain test configuration $2 \ldots \ldots \ldots \ldots$                                       | 105 |

| 6.8  | Op amp open loop gain test configuration 3                                                                     | 106 |

| 6.9  | Op amp open loop gain test configuration 4                                                                     | 107 |

xxvi

## Chapter 1

## Introduction

Operational Amplifiers (Op amps) are one of the most widely used building blocks for analog and mixed-signal systems. They are employed from dc bias applications to high speed amplifiers and filters. General purpose op amps can be used as buffers, summers, integrators, differentiators, comparators, negative impedance converters, and many other applications. With the quick improvements of computer aided design (CAD) tools, advancements of semiconductor modeling, steady miniaturization of transistor scaling, and the progress of fabrication processes, the integrated circuit market is growing rapidly. Nowadays, complementary metal-oxide semiconductor (CMOS) technology has become dominant over bipolar technology for analog circuit design in a mixed-signal system due to the industry trend of applying standard process technologies to implement both analog circuits and digital circuits on the same chip. While many digital circuits can be adapted to a smaller device level with a smaller power supply, most existing analog circuitry requires considerable change or even a redesign to accomplish the same feat. With transistor length being scaled down to a few tens of nanometers, analog circuits are becoming increasingly more difficult to improve upon.

The classic Widlar op amp architecture, originally developed for bipolar devices, has required modification for use with CMOS devices. In particular, it has proved difficult to match the open loop gain of bipolar op amps with CMOS technology [3,4]. This is due to the inherently lower transconductance of CMOS devices as well as the gain reduction due to short channel effects that come into play for submicron CMOS processes. As a result, gain boosting schemes have been reported [5,6] to improve the gain. These gain enhancing methods often require more complicated circuit structures and higher power supply voltage, and may produce a limited output voltage swing. Multiple stage amplifiers may be used for higher gain analog circuit designs. Nevertheless, multistage amplifiers generally are difficult to compensate. Many compensation schemes for multistage amplifiers have been investigated and reported [3–5,7]. Techniques similar to those used in general feedback control systems have been adapted to use with electronic amplifiers. These methods include lead-lag networks, pole splitting, nested Miller compensation as well as signal level variable components. However, most compensation methods require more circuit area and more complex design than the dominant pole approach used in the classic op amp architecture. Special problems of integrated circuit amplifiers which include lack of large sized capacitors, parasitic coupling, and package parasitics and on/off chip load problems make the compensation more difficult than discrete component amplifiers.

The most widely used method of compensating integrated circuit op-amps is undoubtedly pole splitting in which the amplifier stage with the smallest bandwidth is further narrow-banded by a compensating capacitor that creates a well-defined dominant pole that sets both open and closed loop bandwidth of the overall amplifier. This method was featured in the original 741/101 bipolar op-amps designed by Robert Widlar and was widely mimicked in later CMOS op amp designs. This method of compensation is in fact so ubiquitous in the integrated circuit industry that most modern textbooks on integrated circuit op amp design do not include discussion of any alternative methods of compensation.

This thesis is concerned with the compensation techniques for operational amplifiers and will explore new and novel methods of achieving compensation in feedback amplifiers that do not limit the bandwidth of closed loop performance to the same degree that commonly used methods do. Specific tools and methodologies will be developed to allow comparison of the new methods with standard methods of compensation. The proposed active feedforward is used to compensate the multistage operational amplifier with good phase margins as well as drastic improvement of the bandwidth of the amplifier compared to the most widely used pole splitting Miller capacitor compensation approaches.

As mentioned above, the trend for low power applications demands novel op amp architectures. In control and instrumentation applications where high accuracy is required, high gain op amp designs are necessary. Other high-gain CMOS op amps have been investigated in previous work [8–14], but most were unable to achieve gains higher than 100 dB. A few achieved a gain ranging from 120 dB to 130 dB. These CMOS op amp designs use up to 5 cascaded gain stages to achieve the high gain. The highest reported was the simulated 140 dB in [10]. In general, high gain architectures need more complicated compensation to stabilize the op amp and generally require more than one compensation capacitor.

This thesis discusses the design of a high gain, general purpose op amp with the structural simplicity of the classical Widlar architecture. The proposed op amp structure applies composite cascode connections in both the input stage and the second stage to achieve a gain of around 120 dB with low power consumption. The op amp employs the traditional two gain stages followed by a near unity gain buffer stage. This op amp overcomes some limitations of conventional CMOS cascodes by enhancing the gain without using additional bias circuits and requires only a small bias headroom voltage.

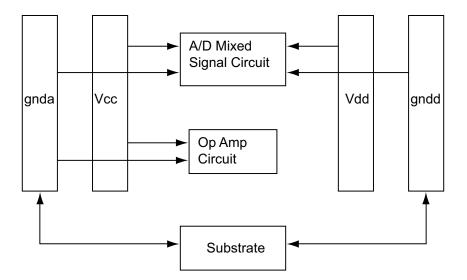

Analog circuit design requires a good understanding of how the system and circuit work. Unlike digital circuitry which works with two distinct states, many parameters are under consideration for analog circuits which work with continuous values. Digital circuit design may be quickly validated on a computer with the help of well-developed CAD tools. Due to the multi-dimensional variables of an analog circuit, any slight change in the analog configuration like current, voltage, a transistor parameter, a device model, a manufacturing process, or a modified layout may cause significantly different performance. In general, this low level device modeling makes analog design more complicated and challenging than digital design. For analog design engineers, a good design methodology including intuition, mathematical methods, and system level simulation combined with device level simulation is essential for creative analog designs. The proposed mixed mode design methodology, which is comprised of mathematical derivation, system level simulation, and device level simulation, will be demonstrated in this thesis.

#### 1.1 Research Contributions

Several original contributions are made and documented in this dissertation. It covers improved frequency compensation for general purpose operational amplifiers and suggests a creative architecture of a high gain low power operational amplifier with composite cascode connections. Moreover, an experimental prototype of the composite cascode op amp has been fabricated in TSMC  $0.25\mu$ m process to verify the low current design exploiting subthreshold transistor operation along with strong inversion operation. In addition, a mixed mode design method combining the system level and device level simulations for innovative analog circuit design is also suggested. A detailed description of the contributions will appear in the corresponding chapters.

#### • Current Compensation Methods Investigation

Though compensation has been a well-studied topic of analog circuit design for many years, an up-to-date comparison and investigation of modern compensation methods has not been done. This survey summarized some popular compensation methods used in op amps and pointed out their advantages and disadvantages. A guide on how to to use different compensation methods based on the output load and other specifications is given.

#### • Feedforward Compensation Method

This proposed feedforward compensation method is fully compatible with the classical general purpose operational amplifier configuration. This architecture also has the advantage of stabilizing the op amp without reducing the bandwidth as much as most commonly used compensation methods do.

• System-Level and Combined Device/Transfer Function Simulation Methodology

4

A design method which integrates intuition, mathematical derivations, system level simulations, and combined device/transfer function simulations is introduced. The proposed system-level and device-level mixed-mode simulation can give insights of creative thoughts, and simplify the analysis by using ideal blocks for some circuitry while providing necessary device model properties.

#### • Stability Analysis of the Feedforward Architecture

A closed loop stability criteria is derived and a design guideline for maximally flat frequency response is suggested to provide circuit stability. Mathematical derivations along with simulation results are presented to correlate the theory with the implementation.

## • MOSFET in Subthreshold Inversion Used for Low Power Op Amp Designs

Operating a MOSFET in the weak inversion region or subthreshold region is very useful for low power applications. A wise choice of the quiescent current as well as the proper  $\frac{W}{L}$  aspect ratios of the transistors can make some of the devices operate in the strong inversion region while other devices operate in the subthreshold region. A current mirror using the composite cascode connection is also proposed to bias the circuit.

### • Architecture of A High gain Composite Cascode Operational Amplifier

A two-gain stage op amp which consists of a differential input composite cascode stage operating at a bias current of 3.65  $\mu$ A and a common source composite cascode second stage provides an open loop gain around 120 dB with 110  $\mu$ W power consumption. With the high output impedance and the low current of the composite cascode connections, a high gain stage is possible with small chip area and power dissipation. This high impedance load also leads to flexible and simple compensation schemes. A phase margin of 43° is achieved using conventional Miller compensation with a capacitor of only 3.5 pF while driving a 100 pF load. A journal paper on this part of the research has been submitted.

• Modified Composite Cascode Operational Amplifiers for Different Applications The proposed op amp which employs composite cascode connections for both differential input stage and second gain stage along with a source follower output stage could be easily modified to adapt to different operating conditions. The second stage could be implemented with a regular common source stage to increase the bandwidth. The source follower stage could be replaced with a class AB output stage for rail-to-rail output swing.

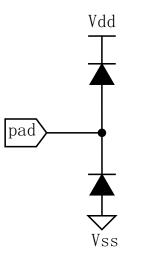

### • Practical Test Methods of High Gain Op Amps

As commonly known, it becomes more difficult to measure the op amp characteristics, especially the open loop gain, as power supply voltages continue to decrease. When the multiplication of input referred noise and the open loop gain of the op amp [6,15] exceeds the power supply voltage, it is difficult to directly test the open loop gain of the op amp. In addition, if the signal magnitude is smaller than the noise magnitude at the input, the output waveform would have little meaning. This work deals with the practical bench test of the open loop gain of the op amp and presents several simple but reliable test methods of op amp open loop gain using typically available bench test equipment.

### 1.2 Dissertation Outline

The research presented in this dissertation covers studies related to the frequency compensation methods of operational amplifiers, gain boosting schemes of operational amplifier design, and low voltage low power analog circuit design. Each chapter presents the analysis of the problem and the development of solutions. A brief outline of each chapter is described below.

Chapter 2 covers the general background information for frequency compensation. The basics of the feedback control stability theory associated with negative feedback amplifiers are reviewed. Other existing frequency compensation methods are discussed with their suitability for different circumstances.

Chapter 3 proposes an active feedforward compensation technique to overcome the bandwidth reduction resulting from commonly used compensation methods like pole splitting. The guidelines of the compensation method are derived through a stability analysis. A mixed mode design methodology is applied to analyze the compensation approach. The design methodology integrates intuition and mathematical analysis along with the system/device level simulation.

In Chapter 4, three different inversion regions of MOSFET operation are reviewed and different op amp gain boosting techniques are introduced. Besides multistage amplifiers with more than three gain stages, conventional cascode, folded cascode, and enhanced impedance methods are investigated along with their advantages and limits. The limit of low voltage analog design is discussed with a few possible low voltage design techniques.

In Chapter 5, the high gain lower power operational amplifier with composite cascode connection is proposed. The subthreshold operation of the MOSFET is emphasized in the composite cascode application. The hardware implementation of the op amp prototype is demonstrated. Measured results are presented along with the simulation results to demonstrate the performance of this op amp design. The variations of the operational amplifier architecture for different circumstances are also discussed in this chapter.

Chapter 6 addresses the issues of testing and characterizing the high gain low voltage op amps. The challenge of measuring the gain of high gain op amps increases as the power supply voltages decrease. Several simple bench test methods are investigated and proposed to characterize the op amp characteristics, in particular the open loop gain. These practical techniques do not require sophisticated instrumentation or complicated lab setup. The setup of the test and the debugging of the practical problems encountered in test are presented.

Lastly, Chapter 7 contains a summary of the research presented. Contributions are enumerated again and possible directions of future research are discussed.

## Chapter 2

# **Frequency Compensation Techniques**

### 2.1 Introduction

In general, operational amplifiers are amplifiers with an open loop gain high enough to ensure the closed loop transfer characteristic with negative feedback is approximately independent of the op amp gain. An adequately high gain is the key requirement of an op amp to utilize the negative feedback configuration.

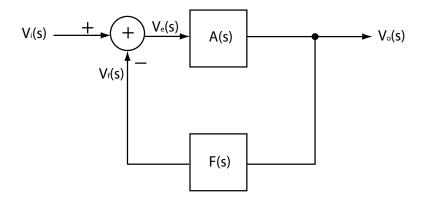

## 2.2 Feedback Circuit Theory

Fig. 2.1 shows a general negative feedback system, where A is the forward gain network and F is the feedback network from the output back to the input terminal. The feedback signal  $V_f(s)$ , which is equal to  $F(s)V_o(s)$ , is subtracted from the source signal  $V_i(s)$  to generate the feedback error signal  $V_e(s)$ , which is the input to A. That is

$$V_e(s) = V_i(s) - F(s)V_o(s).$$

(2.1)

Thus,

$$V_o(s) = A(s)(V_i(s) - F(s)V_o(s))$$

(2.2)

(2.3)

$$G(s) \equiv \frac{V_o(s)}{V_i(s)} = \frac{A(s)}{1 + A(s)F(s)}.$$

(2.4)

Figure 2.1: General negative feedback system

The quantity A(s)F(s) is called the loop gain and is equivalent to the transmission around the feedback loop. As represented by the configuration of a feedback amplifier in Fig. 2.1, A(s) is usually the open loop transfer function and G(s) is the closed loop transfer function. If the loop gain is very high, G(s) is mainly controlled by the feedback network F(s) since  $G(s) \approx \frac{1}{F(s)}$  when  $A(s)F(s) \gg 1$ .

The negative feedback decreases the gain, but it provides a few other benefits such as gain desensitivity, bandwidth extension, impedance modification, and nonlinearity reduction. A sensitivity factor is defined in terms of the differential change of a dependent variable divided by the differential change of an independent variable. Assume G is a function of A, the sensitivity of G relative to A is

$$S_A^G = \frac{\frac{\partial G}{G}}{\frac{\partial A}{A}} = \frac{A}{G} \frac{\partial G}{\partial A}.$$

(2.5)

and

The sensitivity of G in Eq. (2.4) following Eq. (2.5) is derived as

$$S_A^G = \frac{1}{1 + AF}.$$

(2.6)

In the open loop situation, the sensitivity  $S_A^G$  is one since there is no feedback and F equals zero. It is clear that negative feedback reduces the sensitivity of the feedback amplifier to the variations of the amplifier gain A by the factor 1+AF. The overall gain becomes very stable as 1+AF approaches large values.

The sensitivity of G with respect to the changes in the feedback factor F is

$$S_F^G = -\frac{AF}{1+AF} \approx -1. \tag{2.7}$$

The sensitivity  $S_F^G$  is less advantageous compared to  $S_A^G$  since  $S_F^G$  approaches minus one. This result is straightforward since the overall gain is mainly determined by F. To improve the behavior of the system, the feedback network F must be less sensitive to device parameters than the amplifier A. Fortunately, this is the case for most circumstances since the feedback network F usually consists of stable passive devices rather than the active devices of the amplifying element.

Certain configurations of feedback amplifier extend the bandwidth over the open loop amplifier. Assume the amplifier A has a one pole transfer function

$$A(s) = \frac{A_0}{1 + s/p_0},$$

(2.8)

where  $A_0$  is the midband gain of the amplifier and  $p_0$  is the 3-dB bandwidth. Applying Eq. (2.4), the closed loop gain is found to be

$$G(s) = \frac{\frac{A_0}{1+s/p_0}}{1+\frac{A_0F}{1+s/p_0}}$$

(2.9)

$$= \frac{\frac{A_0}{1+A_0F}}{1+\frac{s}{(1+A_0F)p_0}}.$$

(2.10)

The 3-dB bandwidth is increased from  $p_0$  to  $(1 + A_0 F)p_0$  at the cost of a proportional reduction in the gain. Eq. (2.10) implies that the gain-bandwidth product of a one pole system is a constant with feedback, which allows gain and bandwidth to trade off directly by feedback.

Feedback also changes the circuit input and output terminal impedances. With voltage or current quantities as output signals, the feedback networks used to sense the output signal are defined as voltage (shunt) or current (series) connections at the output respectively. With voltage or current quantities provided at the summing terminal, the connections are defined as voltage (series) or current (shunt) types at the input. The voltage (shunt) feedback at the output enhances the output impedance while the current (series) feedback at the output enhances the output impedance. On the other hand, the input impedance to the voltage (series) feedback amplifier is raised while the current (shunt) feedback at the input decreases the input impedance. In conclusion, series feedback increases the impedance while shunt feedback decreases the impedance for both the input and output terminals. Different feedback circuits could be chosen if higher or lower impedance is desired.

Another important effect of a negative feedback system is the reduction of the nonlinearity in analog circuits. There is always nonlinear distortion of the circuits because of the nonlinear amplifying devices. When the nonlinearity is small, the input-output transfer curve is approximately linear. But for large signal swings, the output shows a distorted shape. The change of the small signal gain with the input dc level demonstrates the nonlinear property of the amplifier circuit. The static nonlinearity is denoted as the maximum deviation of the curve from the ideal straight line

$$\% nonlinearity = \frac{\Delta V_{max}}{V_{out,max} - V_{out,min}}.$$

(2.11)

Where  $V_{out,max}$  represents the maximum value of the output signal,  $V_{out,min}$  means the minimum value of the output signal, and  $V_{max}$  is the maximum difference between the actual output curve and the straight line drawn from  $V_{out,min}$  to  $V_{out,max}$ .

We can express the nonlinear transfer function  $V_o = f(V_i)$  by a Taylor series expansion about the quiescent point  $V_{oQ} = f(V_{iQ})$  as

$$V_o = V_{oQ} + (V_i - V_{iQ}) \cdot \frac{dV_o}{dV_i}\Big|_{V_i = V_{iQ}} + \frac{(V_i - V_{iQ})^2}{2!} \cdot \frac{d^2V_o}{dV_i^2}\Big|_{V_i = V_{iQ}} + \cdots \quad (2.12)$$

$$= V_{oQ} + a_1(V_i - V_{iQ}) + a_2(V_i - V_{iQ})^2 + \cdots .$$

(2.13)

Applying a single sinusoidal input around the quiescent point  $(V_{iQ})$  to the nonlinear circuit induces an output spectrum consisting of the input fundamental frequency as well as higher order harmonics. Assuming  $V_i = V_{iQ} + v_i cos(\omega t)$  and applying Eq. (2.13) gives

$$V_{o} - V_{oQ} = a_{1}v_{i}cos(\omega t) + a_{2}v_{i}^{2}\frac{1 + cos(2\omega t)}{2} + a_{3}v_{i}^{3}\frac{3cos(\omega t) + cos(3\omega t)}{4} + \cdots$$

(2.14)

and

$$V_{o} - V_{oQ} = \left(\frac{1}{2}a_{2}v_{i}^{2} + \cdots\right)$$

$$+ \left(a_{1}v_{i} + \frac{3}{4}a_{3}v_{i}^{3} + \cdots\right)cos(\omega t)$$

$$+ \left(\frac{1}{2}a_{2}v_{i}^{2} + \cdots\right)cos(2\omega t)$$

$$+ \left(\frac{1}{4}a_{3}v_{i}^{3} + \cdots\right)cos(3\omega t) + \cdots$$

$$(2.15)$$

Eq. (2.16) can be rewritten in a simplified form

$$V_o - V_{oQ} = A_0 + A_1 \cos(\omega t) + A_2 \cos(2\omega t) + A_3 \cos(3\omega t) \cdots,$$

(2.16)

where the term  $A_0$  shows a dc part introduced to the output signal by the even order harmonics due to nonlinearity and represents the shift from the ideal quiescent output  $V_{oQ}$ .  $A_2$ ,  $A_3$ ,  $\cdots$  represent the amplitudes of higher order harmonic components generated by the nonlinear transfer characteristic. This property is called "harmonic distortion" and this dynamic nonlinearity can be expressed by "total harmonic distortion" (THD) in the following form

$$THD = 10\log \frac{power \ in \ harmonics}{power \ in \ fundamentals}$$

(2.17)

$$= 10 \log \frac{A_2^2 + A_3^2 + \dots}{A_1^2}. \tag{2.18}$$

Harmonic distortion is undesirable in most applications. A THD of about 0.01% (-80 dB) is essential for high quality audio products and a THD around 0.1% (-60 dB) is necessary for video products.

As mentioned, nonlinearity can be regarded as the variation of the small signal gain with the input dc level. Negative feedback keeps the overall closed loop gain nearly constant and almost independent of the amplifier open loop gain. This means that negative feedback reduces distortion resulting from the change in the slope of the amplifier transfer curve. Mathematical analysis of the effect of a feedback system on the nonlinearity of a circuit is very complex and can be found in [16,17]. The second order harmonic typically causes more distortion than the other harmonics and it is one of the reasons that the input differential stage is popularly used in order to get rid of the even harmonics.

#### 2.3 Stability of Feedback Systems

Negative feedback is widely used due to the properties discussed in the preceding section, such as gain desensitization, bandwidth extension, impedance modification, and nonlinearity reduction. Nonetheless, the negative feedback on the frequency response of a circuit may lead to instability. The feedback circuit may oscillate.

The closed loop transfer function of the feedback system shown in Fig. 2.1 is expressed as Eq. (2.4). If F(s) is independent of frequency, it can be simplified as F. Eq. (2.4) can now be expressed as

$$G(s) = \frac{A(s)}{1 + FA(s)}.$$

(2.19)

If  $FA(s)|_{(s=j\omega_1)} = -1$ , the overall gain approaches infinity. In this case, the system is not stable since any small noise will be amplified till the circuit starts to oscillate even without the presence of an input signal. This unstable condition called "Barkhausen's Criteria" is expressed as

$$|FA(j\omega_1)| = 1 \tag{2.20}$$

and

$$\angle FA(j\omega_1) = -180^\circ. \tag{2.21}$$

When  $\angle FA(j\omega_1) = -180^\circ$ , the total phase shift at the inverting input is  $0^\circ$  or  $360^\circ$ since the negative feedback already provides  $180^\circ$  phase shift. This means that the original negative feedback at low frequency becomes positive feedback at some higher frequency  $\omega_1$ . In this situation, if the loop gain at this frequency is greater than unity, the signal will be amplified to cause oscillation.

The necessary and sufficient requirement for a feedback system to be stable is that all the poles of the overall closed loop transfer function have negative real parts. On the Laplace plane, this demonstrates that all the poles of the system are in the left half plane. It may be difficult to analyze the stability of a complex system from the closed loop poles since finding the zeros of the denominator 1+FA(s) of the overall transfer function is complicated. It is more straightforward if we can predict the closed loop stability from the open loop frequency response since the poles of the open loop transfer function are usually known.

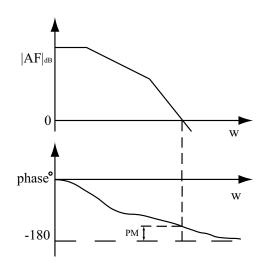

The Nyquist criterion is applied to determine the stability of the feedback system. The Nyquist diagram is a plot which shows the change of the loop gain FA(s) in magnitude and phase with respect to frequency  $\omega$  on a polar plot. If all the poles of the loop gain are in the left half plane, a feedback system is unstable if the Nyquist plot of the loop gain encircles the point (-1, 0). It is clear that Barkhausen's criteria is a simpler version of the Nyquist criterion. Measuring the phase margin (PM) of the open loop gain response is a good quantitative way to express the degree of the stability of a feedback circuit. As shown in Fig. 2.2, the phase margin is specified as  $180^{\circ}$  plus the actual phase shift at the unity gain frequency  $\omega_t$  where  $|FA(j\omega_t)| = 1$ . The PM must be greater than 0° for no oscillation to occur. Gain margin (GM) is defined as the gain difference between the cross over frequency and the phase crossover frequency at which the phase reaches  $-180^{\circ}$ . Both phase margin and gain margin are effective in predicting the stability of a feedback circuit. In the later sections, it is seen that the phase margin is one of the guidelines for designing and compensating operational amplifiers.

Figure 2.2: Phase Margin Plot

Root-Locus is one methodology used to judge the feedback amplifier stability and guide the compensation using frequency domain responses. Root-locus is the locus of poles traced by a feedback system as the constant part of the loop gain varies from zero to infinity. This technique involves the movements of the poles and zeros of the feedback amplifier in the s plane with respect to the variation of the loop gain. Rules have been established [15] to outline the root locus without complicated calculation of the positions of the poles.

#### 2.4 Basic Frequency Compensation Techniques of Operational Amplifiers

The single stage amplifier typically has good frequency response and could achieve a phase margin of  $90^{\circ}$  assuming the gain bandwidth is ten times higher than the single pole. However, the dc gain of the single amplifier is generally not high enough and is even less for submicron CMOS transistors. In general, op amps require at least two gain stages. As a result, op amp circuits have multiple poles. The poles contribute to the negative phase shift and may cause  $\angle FA$  to reach  $-180^{\circ}$  before the unity gain frequency. The circuit will then oscillate due to the negative phase margin. It leads to the necessity of altering the amplifier circuit to increase the phase margin and stabilize the closed loop circuit. This process is called "compensation". By intuition, two different approaches may be taken to stabilize the circuit. The most straightforward way is to make the gain drop faster in order for the phase shift to be less than  $-180^{\circ}$  at the unity gain frequency. This method achieves stability by reducing the bandwidth of the amplifier. The most popular pole splitting method uses this procedure. Another compensation method pushes the phase crossover frequency out by decreasing the total phase shift. In this case, the number of the poles of the op amp needs to be minimized while still providing enough gain. Pushing the phase crossover frequency out is the basic idea of approaches like introducing zeros to cancel the poles or using feedforward paths to improve the phase margin without narrow-banding the bandwidth as much as the pole splitting method does. As shown in later sections and chapters, the feedforward method modifies the open loop transfer function or the closed loop transfer function to increase the phase margin.

#### 2.4.1 Parallel Compensation

Parallel compensation is a classical way to compensate the op amp. A capacitor is connected in parallel to the output resistance of a gain stage of the operational amplifier to modify the pole. It is not commonly used in the integrated circuit due to the large capacitance value required to compensate the op amp, which costs considerable die area.

#### 2.4.2 Pole Splitting - Single Miller Compensation (SMC)

Early in 1967, Widlar designed the LM101/741 [18] op amp which employed the pole splitting frequency compensation method. This method was first used in Bipolar architecture and widely imitated in later CMOS op amp designs. It is covered in many articles and textbooks [15,19]. In 1974, Solomon reported a tutorial study on the monolithic op amp [20] and discussed the pole splitting technique. By putting a compensation capacitor between the input and output nodes of the second inverting stage of the op amp, the dominant pole is created due to Miller [15,21] feedback. This method maintains a high midband gain for the op amp since the capacitor does not affect the dc response of the amplifier. Fig. 2.3 shows the standard SMC topology.

Figure 2.3: SMC

As the transistor gain of the second stage increases, the dominant pole decreases and the nondominant pole increases. In this way the two poles are being split apart and stabilize the feedback amplifiers by greatly narrowing the bandwidth. This simple pole splitting method also introduces a right half plane zero which causes negative phase shift, as a result, the stability is made a little poorer. The zero comes from the direct feedthrough of the input to the output through the Miller capacitor. To eliminate the RHP zero due to the feedthrough and increase the phase margin of the op amp, lead compensation which adds a nulling resistor in series with the compensation capacitor (SMCNR) to increase the impedance of the feedthrough path is reported [4, 15]. Leung and Mok [22] investigated the effect of the nulling resistor to the positions of the poles as well as that of the zero and pointed out the pole splitting would break down if the resistor becomes too big. When the resistor gets very large, there is no pole splitting since the compensation capacitor is actually open circuit. Fig. 2.4 shows the popular SMCNR structure.

Figure 2.4: SMCNR

#### 2.5 Other Multistage Operational Amplifier Compensation Techniques

Many gain boosting schemes have been reported [5] to improve the gain. In general, these gain enhancing designs require more complicated circuit structure and a larger power supply voltage, but generate smaller output swing. As a result, multiple stage amplifiers might be more suitable for low power, low voltage, high density analog circuit designs. The frequency response of the multistage amplifier is not as good as that of the single stage and this amplifier has a higher probability of oscillation in feedback circuits. One popular way to predict the closed loop stability is by measuring the phase margin of the open loop gain response. PM must be greater than 0° for no oscillation to occur. A good performing amplifier will need a PM of about 45° to 60°. Otherwise, the amplifier may exhibit ringing in the time domain and peaking in the frequency domain [15, 23].

#### 2.5.1 Nested Miller Compensation (NMC) and the Variants

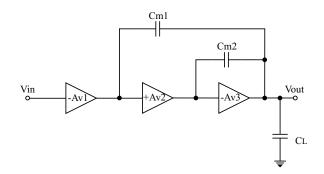

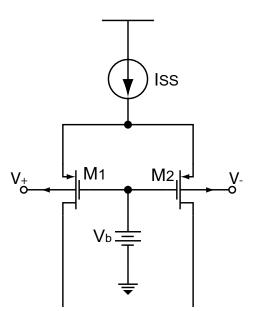

Multistage amplifiers have more poles and zeros than do single stage amplifiers. The frequency response and time response are far more complicated than those of the single stage op amps. As a result, all multistage amplifiers suffer closed loop stability problems. Single Miller compensation is used for the simple two-stage amplifier; while the extended version of the SMC compensation, nested Miller compensation (NMC) [15, 22, 24] is applied to amplifiers with three or more stages. Because of the rapid bandwidth reduction, op amps with more than four stages are rarely investigated. NMC exploits the nested structure of feedback capacitors to cause the pole splitting compensation. There are some drawbacks related to the NMC approach. The total of N-1 nested compensation capacitors must be placed between the dominant node and the other nodes to split the individual poles from the dominant output pole to stabilize an N stage op amp. Fig. 2.5 shows the structure of a three stage NMC op amp. The nesting topology of the compensation capacitor reduces the bandwidth substantially [5, 24, 25]. The specific configuration requires the compound noninverting gain stages to connect to the inverting output stage in order to secure negative feedback for the nested compensation loops. The necessity to drive the compensation capacitors along with the capacitive load requires the output stage to have a high transconductance to attain wide bandwidth and high slew rate. Consequently, elevated power consumption is unavoidable especially for large load capacitor.

Figure 2.5: NMC

To address the bandwidth degradation problem, the variations of the NMC are developed. NMC using nulling resistor (NMCNR) [4,15], reversed nested Miller compensation (RNMC) [19], multipath NMC (MNMC) [5,22,24,26], hybrid NMC (HNMC) [5], nested Gm-C compensation (NGCC) [27] have been presented.

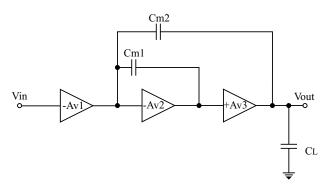

RNMC improves the bandwidth over NMC by the reversed compensation topology compared to NMC as shown in Fig. 2.6.

Figure 2.6: RNMC

The RNMC technique sets the second gain stage negative and the output stage positive. The Miller capacitor loop is around the second stage without connection to the considerable output capacitive load. HNMC combines the NMC and the RNMC topological properties in a multistage (above three) op amp. In this circumstance, the circuit could consist of only inverting amplifier except for the input stage.

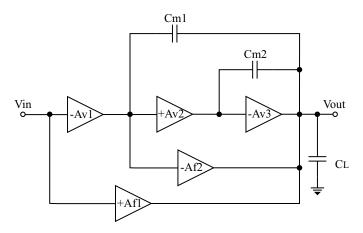

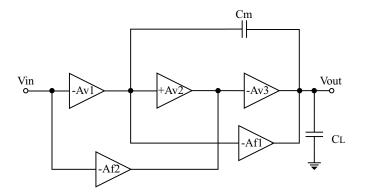

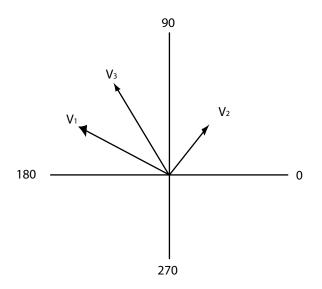

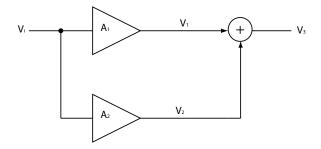

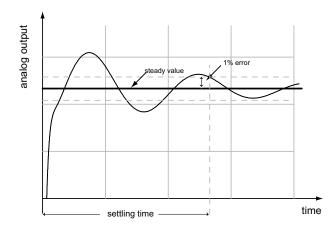

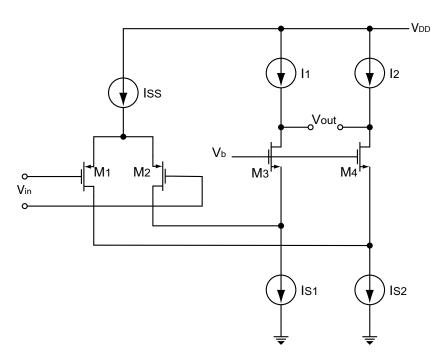

The difference between NMC and MNMC is the added feedforward amplifier stage -Af1 connected between the input of the first stage and the input of the last stage of the multistage op amp as shown in Fig. 2.7. The feedforward stage added can produce a LHP zero to counteract the second nondominant pole to broaden the bandwidth. The increased circuit complexity and power consumption should be considered. Moreover, the pole zero doublets may seriously degrade the settling time of the amplifier [28].

Figure 2.7: MNMC

The difference between NGCC and MNMC is that NGCC replicates the feedforward  $G_m$  N-1 times for an N stage op amp recursively as shown in Fig. 2.8. Compared to MNC, NGCC has simpler stability conditions due to the much simpler transfer function which makes the op amp design more facile.

Figure 2.8: NGCC

The basic idea of most of these variations of the NMC schemes is not to drop the overall bandwidth of the multistage amplifiers by the pole zero cancellation in the passband caused by the feedforward path of the multipath topology. All of those compensation techniques mentioned above use Miller capacitors whose sizes are related to the load capacitor value. The required sizes of the compensation capacitors would escalate with larger capacitive loads which make these techniques not suitable for low area need. The experimental results of the varied versions of NMC showed that the bandwidth does not get improved significantly for considerable capacitive loads [19, 22].

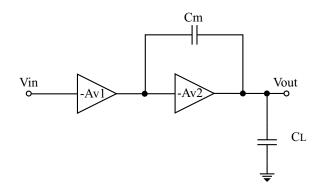

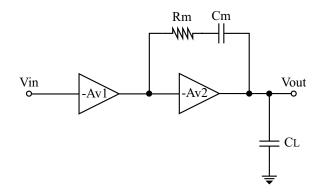

# 2.5.2 Single Miller FeedForward Compensation (SMFFC)

Many compensation techniques mentioned above are not suitable for large load capacitors. The demand for lower power consumption, lower chip integration area, capability for driving large capacitive loads, and stable high gain bandwidth of amplifiers calls for improved frequency compensation patterns. The topologies using a single Miller capacitor in three stage amplifiers could greatly reduce the needed sizes of the compensation capacitors compared to NMC related schemes and result in amplifiers with smaller chip area. The presented SMFFC and the modified SMC with the additional feedforward path from the output of the first stage to the output load stage [27] are designed for a particular three stage amplifier specifically in the case of large capacitive loads. The topology of the SMFFC op amp is represented in Fig. 2.9. Instead of using pole zero cancellation, SMC with one forward path adopts the separate pole approach [22] for compensation in the situation of large capacitive loads. SMFFC employs two forward paths and provide a LHP zero to compensate the first nondominant pole to alleviate the bandwidth reduction and improve the phase margin. The strictly rational selection of gains among the three stages is the key point for this SMFFC scheme. For the gain distribution like  $A_{v1} \gg A_{v2} \ge A_{v3}$ , the second and third poles of the amplifier would be placed at higher frequencies that lead to a coarse single pole system for an easier frequency compensation strategy. The appropriate selection of the moderate gain of the second stage will then decrease the compensation capacitor size. Unfortunately, this method does not truly resolve the compressed gain bandwidth issue due to the super high gain of the first stage and the nature of the pole separation. Gain enhanced feedforward path compensation

Figure 2.9: SMFFC

(GFPC) [29] is much like the modified SMC version with one feedforward path, but for two stage amplifiers.

# 2.5.3 Nonstandard NMC Schemes

The nonstandard NMC topologies have been investigated to deal with the drawbacks with the NMC and MNMC in order to be able to drive large capacitive loads. The reported strategies include damping factor control frequency compensation (DFCFC) [30], embedded RC compensation (ERC) [25], active feedback frequency compensation (AFFC) [31], and dual loop parallel compensation (DLPC) [32, 33]. The ERC duplicates the RC compensation process N-2 times for an N stage op amp. ERC compensation circuits do not load the output stage as NGCC circuit do. The noninverting gain stages are not necessary in ERC as in NMC or the standard variations of NMC. ERC topology extends the bandwidth via the zero pole cancellation through the embedded compensation network without connection to the output load. Usually ERC uses a low gain, high conductance output stage to have the similar loading isolation benefit as the buffer output stage of the Widlar architecture. DFCFC can substantially improve the bandwidth of a three stage amplifier with good frequency and transient responses when driving large capacitive loads. But it is not so effective for small capacitive load applications. Some other compensation methods turn out to be more suitable than DFCFC when driving a small capacitive load.

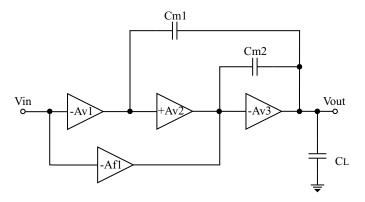

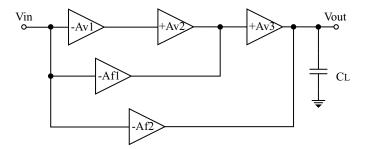

# 2.5.4 No Capacitor Feed Forward (NCFF)

One feedforward compensation scheme for multistage operational transconductance amplifiers with no Miller capacitors is proposed by Thandri and Silva-Martinez [34]. This NCFF method applies the feedforward path as shown in Fig. 2.10 to create LHP zeros. By using the positive phase shift of LHP zeros to cancel the negative phase shift of the poles, a high gain, high bandwidth amplifier with a good phase margin is developed. Thandri does mention some design considerations of the NCFF in the paper. For example, the feedforward and second stage must place the nondominant poles after the overall unity gain frequency of the amplifier to alleviate phase deduction; the pole zero cancellation should happen at high frequencies to achieve better time domain response. Some other constraints of the NCFF scheme not directly specified in the paper should also be recognized. The NCFF is not suitable for big capacitive loads as a result of the main design consideration mentioned. The transient response might be degraded severely by the pole-zero doublets [28]. A good performing amplifier should have both good frequency response and transient response. The complexity of the presence of extra poles and zeros can cause the design of the NCFF scheme to be very difficult and the undesired low frequency pole-zero doublets may lengthen the settling time of the amplifier or even make the closed loop unstable.

Figure 2.10: NCFF

#### 2.5.5 Negative Miller Capacitance Compensation (NMCC)

The negative Miller capacitance compensates high speed CMOS op amps [35] that consists of an operational transconductance amplifier (OTA) and a buffer. The buffer with a dc gain of A is used to detach the OTA from the load. The OTA is compensated with a capacitor  $C_c$  connected between the input and output of the buffer. Assuming the op amp drives a load with a parallel combination of a resistor  $R_L$  and a capacitor  $C_L$ , the effective capacitance seen at the input of the buffer is  $C_{in} = C_c(1-A)$  and  $C_{out} = C_L + C_c(1-\frac{1}{A})$  at the output of the buffer. Since the gain of the buffer is positive and smaller than one, the reflected Miller capacitor  $C_c(1-\frac{1}{A})$ at the output will be negative. The total effective output capacitance is reduced to be smaller than the original load capacitance due to the negative Miller capacitance. NMCC can be applied to drive a large capacitive load. The experimental results show that the NMCC design shifts the first nondominant pole to a higher frequency while keeping the position of the dominant pole almost the same. This NMCC scheme could increase both the bandwidth and phase margin.

Comer et al. [36] proposed a CMOS amplifier bandwidth extension method by utilizing a negative capacitance circuit. Negative capacitance can be generated by active circuitry using the Miller effect. The limitations of current IC technologies restrain the use of inductors and only small capacitors are available. With the innovative negative capacitor idea, compensation practice could shape the frequency response with more freedom.

# 2.6 Conclusion

This chapter introduces the background of feedback systems and the frequency compensation techniques for feedback operational amplifiers. To stabilize op amps, the common techniques are pole splitting and pole zero cancellation using a capacitor and resistor [3,7]. This section discusses and compares the existing methods of achieving compensation for multistage amplifiers. It points out the advantages and disadvantages of the different compensation topologies in order to help the op amp designers better understand and choose the appropriate structure for different circumstances. Some previous solutions are shown to illustrate the design issues related to the respective compensation configuration and to provide the necessary background.

# Chapter 3

# Creative Feedforward Op amp Compensation Design

# 3.1 Introduction

The operational amplifier is probably the most popular building block in analog circuits. As mentioned in chapter 2, the conventional pole splitting method [20] puts a compensation capacitor between the input and output nodes of the second inverting stage of the op amp to break away the two poles due to the Miller feedback. The dominant pole is created to stabilize the feedback amplifiers by further narrowing the small bandwidth. As presented in chapter 2, most modern compensation methods require specific design for the corresponding compensation topology and in general some particular design conditions are imposed. For example, the first gain stage must have a gain much higher than the other stages or the second nondominant pole must be set above the unity gain frequency. These requirements complicate the circuit design and make the compensation configuration not very suitable for the general purpose op amp. A creative compensation methodology which can stabilize the op amp without sacrificing the bandwidth too much but is also compatible with the classical op amp architecture would be useful. This thesis proposes an active feedforward compensation scheme which is suitable for the usual op amp structure with two gain stages followed by a buffer stage. This compensation scheme does not limit the bandwidth of the amplifiers as the most widely used pole splitting Miller capacitor compensation approach does. Instead, the new method stabilizes the feedback amplifiers by increasing the gain bandwidth as well as the phase margin.

A single stage amplifier has good frequency response and good phase margin. But the dc gain of the single amplifier is not high enough and is further reduced by the short-channel effect of submicron CMOS transistors. As a result, a modern high gain op amp requires at least two gain stages. Due to the many poles and zeros of multistage amplifiers, their frequency response and time response are far more complicated than those of single stage op amps. All uncompensated multistage amplifiers suffer closed loop stability problems and need compensation. A multistage op amp with more than three gain stages is uncommon because of the highly increased complexity of compensation. Many compensation schemes for multistage amplifiers have been investigated and reported [3–5,7]. Chapter 2 of this thesis gives a detailed survey of the current compensation methods and points out their suitability for different situations.

Pole splitting, the most often used compensation technique, rolls off the gain before the phase lag becomes too great. The common method of pole splitting is to use a compensation capacitor between the input and output nodes of the second inverting stage of the op amp. The dominant pole is created due to Miller feedback. The negative Miller capacitance compensation method (NMCC) employs the idea to compensate a high speed CMOS op amp [35] with negative capacitance generated from the buffer stage by the Miller effect to reduce the original output load capacitance.